http://mtca.desy.de

# Zone 3 Connector Pin Assignment Recommendation for Analog Applications for AMC/µRTM Boards in the MTCA.4 standard

### FEATURES

MTCA.4 management zone:

Power, I<sup>2</sup>C, optional JTAG support

Analog signal transmission zone:

- 32 channel DC-coupled differential input signals

- · 4 channel DC-coupled differential output signals

Digital clock signal transmission zone:

- · 2 AC-coupled differential inputs for low-jitter clock signals

- 1 LVDS output clock signal

User signal transmission zone:

- · 6 LVDS inputs / outputs for user-configuration

- 3 LVDS outputs with fixed output direction

- Optional dual high-speed link

#### Zone shielding:

· Supports ground shielding between zones

# APPLICATIONS

- AMC / µRTM board design in MTCA.4 standard

- · Multi-channel analog-to-digital converters

- · Multi-channel signal shaper

- · Multi-channel sensor readout and output

- · Analog signal conditioning boards

- · Low-jitter clock signal sampling and clock recovery

### **GENERAL DESCRIPTION**

This Class A2.1 pin assignment definition of the Zone 3 connector in the MTCA.4 standard is a recommendation mainly for AMC and  $\mu RTM$  boards transferring a high number of analog signals over the Zone 3 connector. This analog class is designed for two three row ADF Zone 3 connectors and AMC modules having an FPGA. The main goal is to classify the undefined Zone 3 pin assignment for applications to achieve a high compatibility between AMC and  $\mu RTM$  boards.

This Class A2.1 pin assignment requires a common µRTM management implementation to make AMC and µRTM boards compatible. Appropriate management interface templates for this Class are available on http://mtca.desy.de.

# AMC ZONE 3 CONNECTOR PIN ASSIGNMENT RECOMMENDATION

| Class A2.1 / Zone      |     |    | а         | b         | C       | d       | e       | f       |

|------------------------|-----|----|-----------|-----------|---------|---------|---------|---------|

|                        | _   |    |           |           |         |         |         |         |

| MTCA.4 management      | J30 | 1  | PWRA1     | PWRB1     | PS#     | SDA     | TCK     | TDO     |

| in or it indiadgomonic |     | 2  | PWRA2     | PWRB2     | MP      | SCL     | TDI     | TMS     |

| Standard Gbit-Link     |     | 3  | SFP-CLK+  | SFP-CLK-  | SFP-RX+ | SFP-RX- | SFP-TX+ | SFP-TX- |

| User-configuration     |     | 4  | D3+       | D3-       | D4+     | D4-     | D5+     | D5-     |

| Oser-conliguration     |     | 5  | D6+       | D6-       | D7+     | D7-     | D8+     | D8-     |

| Digital fixed I/O      |     | 6  | AMC_TCLK+ | AMC_TCLK- | OUT0+   | OUT0-   | OUT1+   | OUT1-   |

| Shielding              |     | 7  | gnd       | gnd       | gnd     | gnd     | gnd     | gnd     |

| Digital clock inputs / |     | 8  | AMC_CLK0+ | AMC_CLK0- | DAC3+   | DAC3-   | DAC2+   | DAC2-   |

| Analog Signals         |     | 9  | RTM_CLK0+ | RTM_CLK0- | DAC1+   | DAC1-   | DAC0+   | DAC0-   |

| Analog Olghais         |     | 10 | RTM_CLK1+ | RTM_CLK1- | CH31+   | CH31-   | CH30+   | CH30-   |

|                        |     |    |           |           |         |         |         |         |

|                        | J31 | 1  | CH29+     | CH29-     | CH28+   | CH28-   | CH27+   | CH27-   |

|                        |     | 2  | CH26+     | CH26-     | CH25+   | CH25-   | CH24+   | CH24-   |

|                        |     | 3  | CH23+     | CH23-     | CH22+   | CH22-   | CH21+   | CH21-   |

|                        |     | 4  | CH20+     | CH20-     | CH19+   | CH19-   | CH18+   | CH18-   |

| Analog signals         |     | 5  | CH17+     | CH17-     | CH16+   | CH16-   | CH15+   | CH15-   |

| Analog signals         |     | 6  | CH14+     | CH14-     | CH13+   | CH13-   | CH12+   | CH12-   |

|                        |     | 7  | CH11+     | CH11-     | CH10+   | CH10-   | CH9+    | CH9-    |

|                        |     | 8  | CH8+      | CH8-      | CH7+    | CH7-    | CH6+    | CH6-    |

|                        |     | 9  | CH5+      | CH5-      | CH4+    | CH4-    | CH3+    | CH3-    |

|                        |     | 10 | CH2+      | CH2-      | CH1+    | CH1-    | CH0+    | CH0-    |

### ZONE DESCRIPTION

Table 1 : Pin assignment of Class A2.1, AMC side view

This Class A2.1 is mainly used for data acquisition applications having a high number of analog signal channels. As depicted in Table 1, the zones in the analog Class A2.1 consists of a management zone, user zone, digital clock zone and a zone for analog differential signals.

The management zone (J30 row 1-2) is reserved for the  $\mu$ RTM management in the MTCA.4 standard. The user zone (J30 row 4-5) houses input and output signals in LVDS, CMOS or open collector (OC) level, which can be used for general purpose, e.g. I<sup>2</sup>C communication for slow board diagnostics. To achieve a high compatibility between AMC and  $\mu$ RTM boards, these inputs and outputs should be connected and programmable in direction and signal type, preferable by an FPGA located on the AMC side.

The user zone (J30 row 6) houses LVDS output signals with fixed signal direction to provide a stable timing signal AMC\_TCLK, which is the splitted TCLKA and two general purpose output signals OUT0 and OUT1 to the  $\mu$ RTM typically not driving from the FPGA. The user zone (J30 row 3) offers one high speed link for general purposes. In case of not using the high speed link it is recommended to switch it off. The digital clock zone (J30 row 8-9) offers 2 digital AC-coupled differential inputs and 1 LVDS output AMC\_CLK0 for low-jitter clock signals. RTM\_CLK0 is reserved for the main ADC clock domain. The second clock RTM\_CLK1 is optional and can be used for DACs or ADCs.

The analog zone (J31) consists of up to 32 analog DC-coupled differential signal inputs (CHx+, CHx-) and 4 DC-coupled differential outputs signals for current driven DACs (DACx+, DACx-).

# SEQUENCE OF SIGNAL OCCUPATION

To achieve a high compatibility between AMC and µRTM boards we recommend to use the sequence for the signal occupation in each zone starting from minimum label to the maximum in each zone. The signal distribution and filling sequence of the clock and analog signals over Zone 3 is chosen for having a high isolation between these signals. Taken into account, that analog applications may need also a fast digital serial connection (J30 row 3), the user zone starts at J30 4ab, where a user I<sup>2</sup>C bus for basic diagnostics can be placed. Digital output signals are located in (J30 row 6). (RTM\_CLK1+, RTM\_CLK1-) is reserved for a second clock domain for DACs or ADCs.

| Analog inputs:               | (CH0+, CH0-), (CH1+, CH1-),, (CH31+, CH31-)                      |

|------------------------------|------------------------------------------------------------------|

| Analog outputs:              | (DAC0+, DAC0-), (DAC1+, DAC1-),, (DAC3+, DAC3-)                  |

| Digital input signals:       | (RTM_CLK0+, RTM_CLK0-) reserved for main ADC clock domain        |

|                              | (RTM_CLK1+, RTM_CLK1-) optionally reserved for DAC or ADC clocks |

| Digital output signals:      | (AMC_CLK0+, AMC_CLK0-)                                           |

| User - input/output signals: | (D3+,D3-), (D4+,D4-),, (D8+, D8-)                                |

# AMC ZONE 3 CONNECTOR ELECTRICAL SPECIFICATION RECOMMENDATION

| Class A2.1 / Zone      |     |    | а                        | b                        | c                        | d                        | e                        | f                     |

|------------------------|-----|----|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|-----------------------|

|                        | J30 | 1  | PWRA1                    | PWRB1                    | PS#                      | SDA                      | тск                      | TDO                   |

| MTCA.4 management      |     | 2  | PWRA2                    | PWRB2                    | MP                       | SCL                      | TDI                      | TMS                   |

| Standard Gbit-Link     |     | 3  | LVDS - I                 | LVDS - I                 | CML - I                  | CML - I                  | CML - O                  | CML - O               |

| User-configuration     |     | 4  | LVDS / LVCMOS / OC - I/O | LVDS / LVCMOS / OC -  |

| User-conliguration     |     | 5  | LVDS / LVCMOS / OC - I/O | LVDS / LVCMOS / OC -  |

| Digital fixed I/O      |     | 6  | LDVS - O                 | LDVS - O              |

| Shielding              |     | 7  | gnd                      | gnd                      | gnd                      | gnd                      | gnd                      | gnd                   |

| Digital clock inputs / |     | 8  | LDVS - O                 | LDVS - O                 | Differential 0 - ±20mA   | A / 0 - ±1V / Ο, 100Ω    | Differential 0 - ±20m/   | A / 0 - ±1V / Ο, 100Ω |

| Analog Signals         |     | 9  | Differential AC-coupled, | ±350mV±1V / Ι, 100Ω      | Differential 0 - ±20mA   | A / 0 - ±1V / Ο, 100Ω    | Differential 0 - ±20m/   | A / 0 - ±1V / Ο, 100Ω |

|                        | _   | 10 | Differential AC-coupled, | ±350mV±1V / Ι, 100Ω      | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω         |

|                        | J31 | 1  | Differential 0 -         | ±1V / Ι. 100Ω            | Differential 0 -         | ±1V / Ι. 100Ω            | Differential 0 -         | ±1V / Ι. 100Ω         |

|                        |     | 2  | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω         |

|                        |     | 3  | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω         |

|                        |     | 4  | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω         |

| Analog signals         |     | 5  | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω         |

| Analog signals         |     | 6  | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω         |

|                        |     | 7  | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω         |

|                        |     | 8  | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω         |

|                        |     | 9  | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω         |

|                        |     | 10 | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω            | Differential 0 -         | ±1V / Ι, 100Ω         |

Table 2: Electrical specification of Class A2.1 ("I"=input (µRTM to AMC), "O"=output (AMC to µRTM)), AMC side view

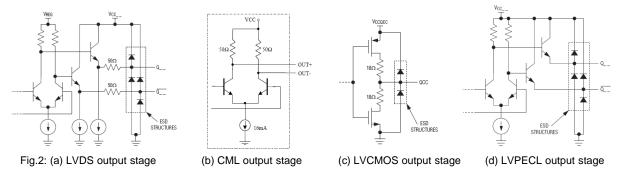

The signals of the management zone are defined in PICMG MTCA.4 R1.0, Section 4. The high speed link signals (J30 row 3) have fixed signal direction, level of LVDS for an external clock and CML for receiving and transmitting data. Digital levels in the user zone (J30 row 3-4) are LVDS, LVCMOS or open collector (OC) outputs typically provided by an FPGA. LVCMOS or OC outputs needs on the  $\mu$ RTM a supply voltage adjust mechanism controlled by the AMC management. Using I<sup>2</sup>C communication open collector signals in the user zone are assumed to be terminated on the  $\mu$ RTM side. Digital output signals (J30 row 6) and signals of the clock and analog zone (J30 row 8,9,10) have fixed direction. Digital low-jitter clock input signals (J30 9ab, 10ab) are AC-coupled differential signals in the range of 350mV... 1V. This allows the usage of LVDS, LVPECL, CML and other digital low-jitter signal types. The AC-coupling is done before termination on the AMC-side. Signals of the analog zone (J31) are typically in the range of -1V...+1V and have to be differentially matched by 100 Ohms defined by the ADF connector. For optimal performance the analog outputs should be current driven typically in the range of -20mA...+20mA.

# AMC MODULE AND µRTM PROTECTION

According to the PICMG MTCA.4 R1.0, section 3.5.7, ¶79 the insertion and extraction process of an  $\mu$ RTM need an application specific quiesce action, e.g. no action, isolation of signals or powering off the AMC controlled by the MMC. All AMC output signals with fixed direction of Class A2.1 compatible modules have to be disabled via buffers on the AMC side controlled by the MMC. In addition these signals can be disabled or enabled application specific independent of the MMC protection mechanism.

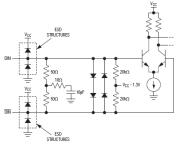

Modern FPGAs offer a wide range of single- and differential ended input and output levels using different supply voltage banks. Here LVDS, LVCMOS\_25, CML and open collector signaling with 2.5V power supply in the user zone are of interest. FPGA signals can be isolated during the insertion process, other devices rather not. Most of the devices have inputs and outputs protected with diodes intended only for short transient currents, as depicted in Fig.1. In case of an unpowered  $\mu$ RTM, active high state output stages of the AMC module will continuously dissipate power into the  $\mu$ RTM protection diodes. Depending on the output stages of Fig.2 the maximum short-to-GND currents are given by 40mA for LVDS, 50mA for CML, 200mA for LVCMOS\_25 and approx. 2.5mA for OC\_25 (open collector). AMC and  $\mu$ RTM boards for analog applications, that uses analog voltages in the range of -1V...1V must have a N=2 module hardware keying according to the MTCA.4 standard listed in Table 3, respectively N=3 when using LVCMOS\_25 in the user zone.

Fig.1 : Differential input stage

| N | Data Signal in Volts |

|---|----------------------|

| 1 | LVDS                 |

| 2 | $0 - \pm 1$          |

| 3 | >±1-±3.3             |

| 4 | >±3.3-±10            |

| 5 | >±10                 |

| 6 | Reserved             |

| 7 | Reserved             |

| 8 | Reserved             |

Table 3: Mechanical module keying

Table 4 shows the AMC output signals, which have to be isolated, disabled or tri-stated on the AMC side in Class A2.1. Depending on the signal type the recommended protection method is listed. The FPGA gets the disabling information directly from MMC.

| Idle state, AC-coupled  | (SFP-TX+, SFP-TX-) state should be set to IDLE mode by FPGA on the AMC and $\mu$ RTM. To remove common mode CML-levels, an AC-coupling has to be used on each transceiver side.                                                                                                                                                                                 |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disabling via FPGA      | FPGA signals of the user zone (J30 row 4,5) can be disabled via FPGA itself.                                                                                                                                                                                                                                                                                    |

| Disabling via buffer    | LDVS output signals (J30 row 4,5) with fixed signal direction have to be disabled by using a buffer with output enable. The disabling information is provided by the MMC. Depending on the application the buffer speed and jitter performance has to be chosen.                                                                                                |

| DAC quiescent condition | The DAC quiescent condition for a current driven DAC is a zero output current or power down. To reduce transient voltages for an unmatched current driven DAC output in case of an unplugged $\mu$ RTM, a matching network on the AMC and $\mu$ RTM is recommended. Isolating DAC outputs via analog buffers will degrade the performance and is not an option. |

Ein Forschungszentrum der Helmholtz-Gemeinschaft

http://mtca.desy.de

| Class A2.1 / Zone      |     |    | а                    | b                    | C                          | d                          | е                          | f                         |

|------------------------|-----|----|----------------------|----------------------|----------------------------|----------------------------|----------------------------|---------------------------|

|                        |     |    |                      |                      |                            |                            |                            |                           |

| MTCA.4 management      | J30 | 1  |                      |                      |                            |                            |                            |                           |

| in or a management     |     | 2  |                      |                      |                            |                            |                            |                           |

| Standard Gbit-Link     |     | 3  |                      |                      | Idle state, RTM AC-coupled | Idle state, RTM AC-coupled | Idle state, AMC AC-coupled | Idle state, AMC AC-couple |

| User-configuration     |     | 4  | Disabling via FPGA   | Disabling via FPGA   | Disabling via FPGA         | Disabling via FPGA         | Disabling via FPGA         | Disabling via FPGA        |

| User-conliguration     |     | 5  | Disabling via FPGA   | Disabling via FPGA   | Disabling via FPGA         | Disabling via FPGA         | Disabling via FPGA         | Disabling via FPGA        |

| Digital fixed I/O      |     | 6  | Disabling via Buffer | Disabling via Buffer | Disabling via Buffer       | Disabling via Buffer       | Disabling via Buffer       | Disabling via Buffer      |

| Shielding              | 1   | 7  |                      |                      |                            |                            |                            |                           |

|                        |     | 8  | Disabling via Buffer | Disabling via Buffer | DAC quiescent condition    | DAC quiescent condition    | DAC quiescent condition    | DAC quiescent condition   |

| Digital clock inputs / |     | 9  |                      |                      | DAC quiescent condition    | DAC quiescent condition    | DAC quiescent condition    | DAC quiescent condition   |

| Analog Signals         | 1   | 10 |                      |                      |                            | ·                          |                            |                           |

|                        |     |    |                      |                      |                            |                            |                            |                           |

|                        | J31 | 1  |                      |                      |                            |                            |                            |                           |

|                        | ĺ.  | 2  |                      |                      |                            |                            |                            |                           |

|                        | ĺ.  | 3  |                      |                      |                            |                            |                            |                           |

|                        | 1   | 4  |                      |                      |                            |                            |                            |                           |

|                        | ĺ.  | 5  |                      |                      |                            |                            |                            |                           |

| Analog signals         |     | 6  |                      |                      |                            |                            |                            |                           |

|                        |     | 7  |                      |                      |                            |                            |                            |                           |

|                        | 1   | 8  |                      |                      |                            |                            |                            |                           |

|                        | 1   | 9  |                      |                      |                            |                            |                            |                           |

|                        | 1   | 10 |                      |                      |                            |                            |                            |                           |

Table 4: Quiescent signal conditions of Class A2.1, AMC side view

After inserting the  $\mu$ RTM a compatibility check of the Zone 3 has to performed according to the MTCA.4. After successful acceptance, the  $\mu$ RTM payload power can be switched on. If an  $\mu$ RTM is extracted via hot-swap handle, the  $\mu$ RTM has to be switched off via MMC and the AMC has to set the Zone 3 signals into the disabled state, as well after power cuts and failures. All  $\mu$ RTM output signals do not have to be isolated, because they are powered down during the insertion process. Isolating analog or low-jitter clock signals will degrade their performance and is no option in this class.

### **ZONE 3 GROUNDING, SHIELDING AND TERMINATION**

Each additional pin, which can be grounded on the AMC or  $\mu$ RTM side will increase the signal isolation for a given Zone 3 connector. Grounding both sides will improve the robustness of the AMC and  $\mu$ RTM against EMI distortions crossing the Zone 3. Unused input signals should be in general terminated on the receiver side. They must provide a defined default electrical state defined by the receiver side to avoid oscillations of the following circuit sections. The following guideline should be used if the AMC or the  $\mu$ RTM does not support a signal function.

| Standard Gbit Link:   | If the µRTM do no<br>If the AMC do no                                                                                                                                                                                                                                                                          | tt support SFP, the SFP-CLK and SFP-Rx signal of the AMC should be open on the μRTM side.<br>tt support SFP, the SFP-Tx signal of the AMC should be terminated on the μRTM side.<br>tt support SFP, the AMC should terminate SFP-CLK and SFP-Rx.<br>tt support SFP, the AMC signal SFP-Tx should be open.                                                                                                              |  |  |  |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| User configuration:   | The µRTM should let all unused signals open.<br>The AMC should let all unused signals open.                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Digital fixed I/O:    | If the μRTM do not support the signal function, the μRTM should terminate signals of this group.<br>If AMC_TCLK, OUT0 or OUT1 is not used (implemented) by the AMC, it should let them open.<br>If the μRTM support the signal function it has to provide a default logic state for the signals OUT0 and OUT1. |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Digital clock inputs: | Unused digital clock inputs should be grounded on the µRTM side, signals are AC-coupled on the AMC side.<br>Unused digital clock inputs should be terminated on the AMC side.                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Analog inputs:        | Unused analog A                                                                                                                                                                                                                                                                                                | Unused analog AC-input or DC-input ports should be grounded on the $\mu$ RTM.<br>Unused analog AC-input or DC-input ports should be shorted on the $\mu$ RTM rear signal inputs to avoid oscillations at Zone 3.<br>Unused analog AC-input or DC-input ports can be open, terminated or grounded on the AMC side:                                                                                                      |  |  |  |  |  |  |  |

|                       | Open<br>Terminated<br>(*) Grounded                                                                                                                                                                                                                                                                             | <ul> <li>Recommended, especially if space and routing for a termination degrade the performance.</li> <li>Can be used if space and routing for a termination do not degrade the performance.</li> <li>The AMC may only ground them if a functional or electrical compatibility check of Zone 3 is used.<br/>The robustness of boards against EMI is improved, but only compatible boards will be activated.</li> </ul> |  |  |  |  |  |  |  |

| Analog outputs:       | Unused current driven DACs should be grounded on the µRTM.<br>Unused analog outputs should be grounded on the AMC.                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

http://mtca.desy.de

Table 5 and Table 6 shows the signal termination if the AMC, respectively  $\mu$ RTM does not support a signal function. In case of not using the high speed link it should be switched off to avoid crosstalk onto the  $\mu$ RTM. Unused AC-input or DC-input ports should be open. Their rear signal inputs on the  $\mu$ RTM should be shorted to avoid oscillations at Zone 3. IF unused AC-input or DC-input ports are grounded to improve the EMI robustness only compatible boards will be activated via E-keying.

| Class A2.1 / Zone      |     |    | а             | b                         | c            | d                           | e    | f                                 |

|------------------------|-----|----|---------------|---------------------------|--------------|-----------------------------|------|-----------------------------------|

| AMC side               |     |    |               |                           |              |                             |      |                                   |

| MTCA.4 management      | J30 | 1  | PWRA1         | PWRB1                     | PS#          | SDA                         | TCK  | TDO                               |

| MTCA.4 management      |     | 2  | PWRA2         | PWRB2                     | MP           | SCL                         | TDI  | TMS                               |

| Standard Gbit-Link     | ]   | 3  | differ        | ential terminated         | diffe        | erential terminated         | open | open                              |

| User-configuration     |     | 4  | open          | open                      | open         | open                        | open | open                              |

| Usel-conliguration     |     | 5  | open          | open                      | open         | open                        | open | open                              |

| Digital fixed I/O      |     | 6  | open          | open                      | open         | open                        | open | open                              |

| Shielding              |     | 7  | gnd           | gnd                       | gnd          | gnd                         | gnd  | gnd                               |

| Digital clock inputs / |     | 8  | open          | open                      | gnd          | gnd                         | gnd  | gnd                               |

| Analog Signals         |     | 9  | differ        | ential terminated         | gnd          | gnd                         | gnd  | gnd                               |

| Androg eignale         |     | 10 | differ        | ential terminated         | open / diffe | erential terminated / gnd * | open | / differential terminated / gnd * |

|                        |     |    |               |                           |              |                             |      |                                   |

|                        | J31 | 1  | open / differ | ential terminated / gnd * | open / diffe | erential terminated / gnd * | open | / differential terminated / gnd * |

|                        |     | 2  | open / differ | ential terminated / gnd * | open / diffe | erential terminated / gnd * | open | / differential terminated / gnd * |

|                        |     | 3  | open / differ | ential terminated / gnd * | open / diffe | erential terminated / gnd * | open | / differential terminated / gnd * |

|                        |     | 4  | open / differ | ential terminated / gnd * | open / diffe | erential terminated / gnd * | open | / differential terminated / gnd * |

| Analog signals         |     | 5  | open / differ | ential terminated / gnd * | open / diffe | erential terminated / gnd * | open | / differential terminated / gnd * |

| / maiog signals        |     | 6  | open / differ | ential terminated / gnd * | open / diffe | erential terminated / gnd * | open | / differential terminated / gnd * |

|                        |     | 7  | open / differ | ential terminated / gnd * | open / diffe | erential terminated / gnd * | open | / differential terminated / gnd * |

|                        |     | 8  | open / differ | ential terminated / gnd * | open / diffe | erential terminated / gnd * | open | / differential terminated / gnd * |

|                        |     | 9  | open / differ | ential terminated / gnd * | open / diffe | erential terminated / gnd * | open | / differential terminated / gnd * |

|                        |     | 10 | open / differ | ential terminated / gnd * | open / diffe | erential terminated / gnd * | open | / differential terminated / gnd * |

Table 5: Signal termination in Class A2.1 if the AMC does not support a signal function, AMC side view

| Class A2.1 / Zone      |     |    | а            | b          | c    | d                       | e    | f                       |

|------------------------|-----|----|--------------|------------|------|-------------------------|------|-------------------------|

| RTM side               |     |    |              |            |      |                         |      |                         |

| MTCA.4 management      | J30 | 1  | PWRA1        | PWRB1      | PS#  | SDA                     | TCK  | TDO                     |

| WITCA.4 management     |     | 2  | PWRA2        | PWRB2      | MP   | SCL                     | TDI  | TMS                     |

| Standard Gbit-Link     |     | 3  | open         | open       | open | open                    |      | differential terminated |

| User-configuration     |     | 4  | open         | open       | open | open                    | open | open                    |

| User-conliguiation     |     | 5  | open         | open       | open | open                    | open | open                    |

| Digital fixed I/O      |     | 6  | differential | terminated |      | differential terminated |      | differential terminated |

| Shielding              |     | 7  | gnd          | gnd        | gnd  | gnd                     | gnd  | gnd                     |

| Digital clock inputs / |     | 8  | differential | terminated | gnd  | gnd                     | gnd  | gnd                     |

| Analog Signals         |     | 9  | gnd          | gnd        | gnd  | gnd                     | gnd  | gnd                     |

| Analog Olghais         |     | 10 | gnd          | gnd        | gnd  | gnd                     | gnd  | gnd                     |

|                        |     |    |              |            |      |                         |      |                         |

|                        | J31 | 1  | gnd          | gnd        | gnd  | gnd                     | gnd  | gnd                     |

|                        |     | 2  | gnd          | gnd        | gnd  | gnd                     | gnd  | gnd                     |

|                        |     | 3  | gnd          | gnd        | gnd  | gnd                     | gnd  | gnd                     |

|                        |     | 4  | gnd          | gnd        | gnd  | gnd                     | gnd  | gnd                     |

| Analog signals         |     | 5  | gnd          | gnd        | gnd  | gnd                     | gnd  | gnd                     |

| Analog signals         |     | 6  | gnd          | gnd        | gnd  | gnd                     | gnd  | gnd                     |

|                        |     | 7  | gnd          | gnd        | gnd  | gnd                     | gnd  | gnd                     |

|                        |     |    |              | gnd        | gnd  | gnd                     | gnd  | gnd                     |

|                        | Į   |    | gnd          | gnd        | gnd  | gnd                     | gnd  | gnd                     |

|                        |     | 10 | gnd          | gnd        | gnd  | gnd                     | gnd  | gnd                     |

Table 6: Signal termination in Class A2.1 if the µRTM does not support a signal function, µRTM side view

# COMPATIBILITY TO ANALOG CLASS A1.1

Class A2.1 boards are not compatible to other classes. For test purpose with limited functionality, AMC and  $\mu$ RTM boards can be used between Class A1.1 and Class A.2.1. In this case the signals RTM\_CLK1, CH30, CH31, CH1, CH7, CH13, CH19, CH25 should be unused or isolated on the  $\mu$ RTM side. RTM\_CLK1, RTM\_CLK2, RTM\_CLK3, RTM\_CLK5 on Class A1.1 compatible  $\mu$ RTM should be unused or isolated.

# **REVISION CHANGES AND HISTORY**

| 2014/03                                | <ul> <li>Introduce a new analog Class for a high number of up to 32 analog signals over Zone 3.</li> <li>For simplification Class A2.1 compatible boards are not compatible to Class A1.1.</li> <li>Making Class A2.1 compatible to Class A1.1 is only possible for a small number of channels.</li> </ul> |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2014/03 (Rev.A.1)                      | : - To simplify the Class usage the filling order of CHx signals in J31 is simplified compared to Class A1.1.<br>A minor signal crosstalk degradation by approx. 10dB was accepted by TEWS.                                                                                                                |

| 2014/01 (Rev.A.1)<br>2014/01 (Rev.A.1) | : - For time domain gating applications on the μRTM the AMC_CLK0 signal from AMC to μRTM is available.<br>: - BoF group1 Zone 3 pin assignment (Class recommendation) Rev.A.1. to be confirmed.                                                                                                            |